基于 VHDL 的 Vivado2017.4 使用教程

新建工程

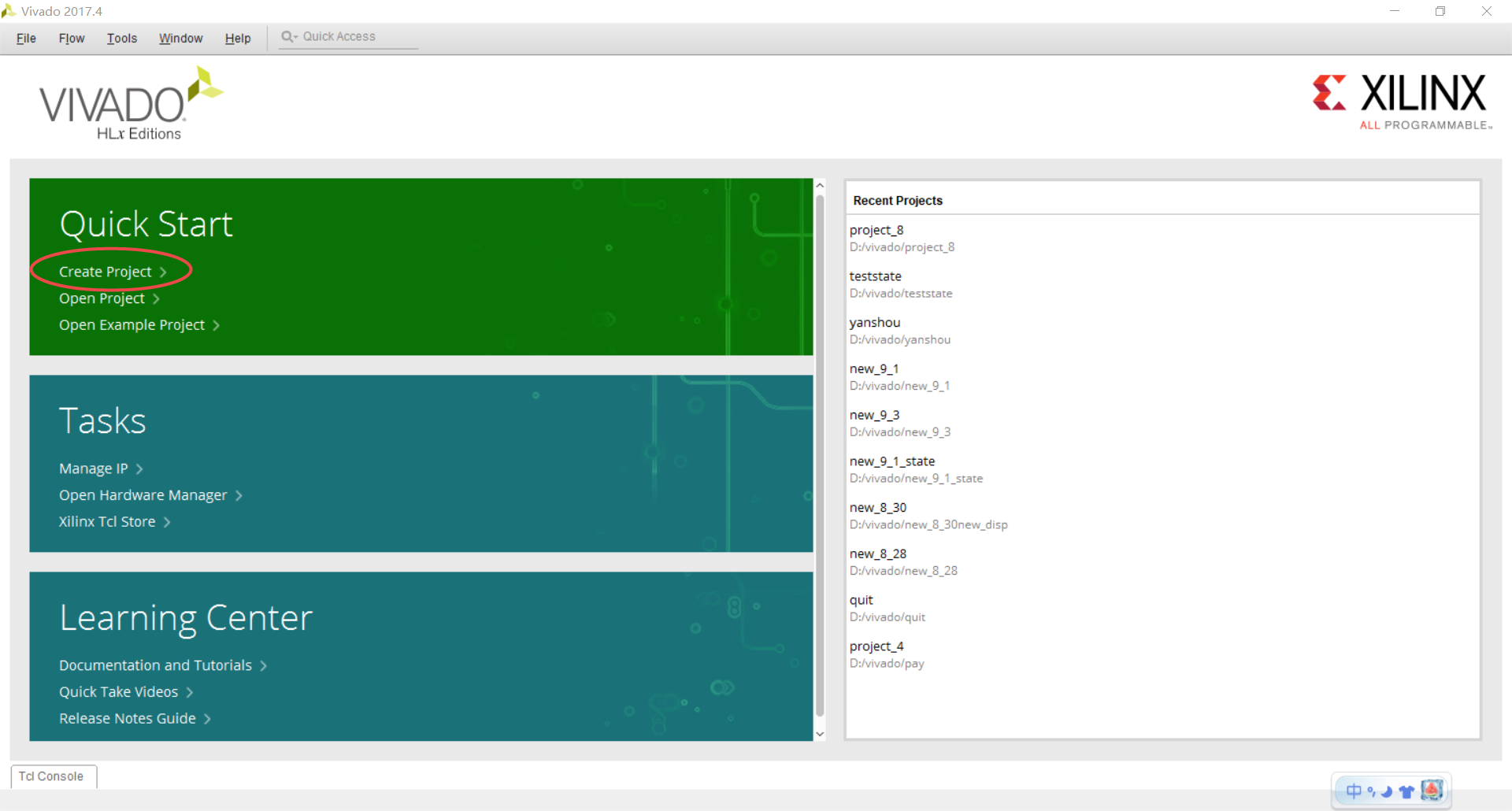

首先打开vivado2017.4

点击create project

点击next

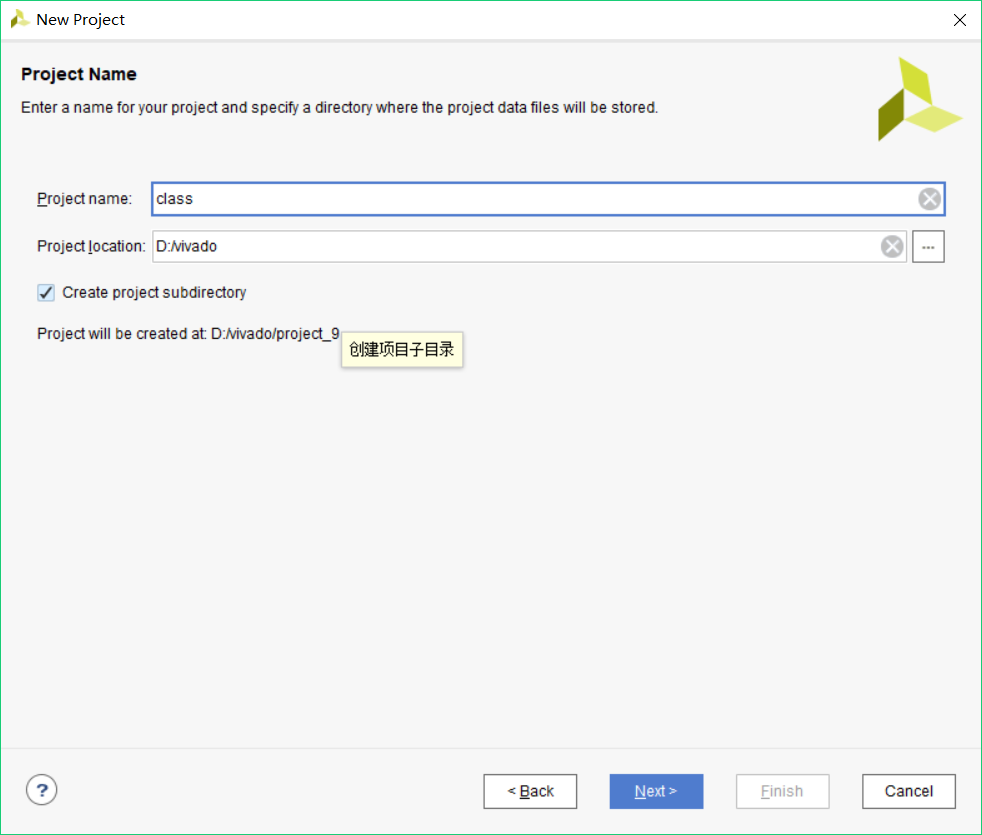

为新建的工程起名字,路径和名字都不要有中文

起好名字后点击next

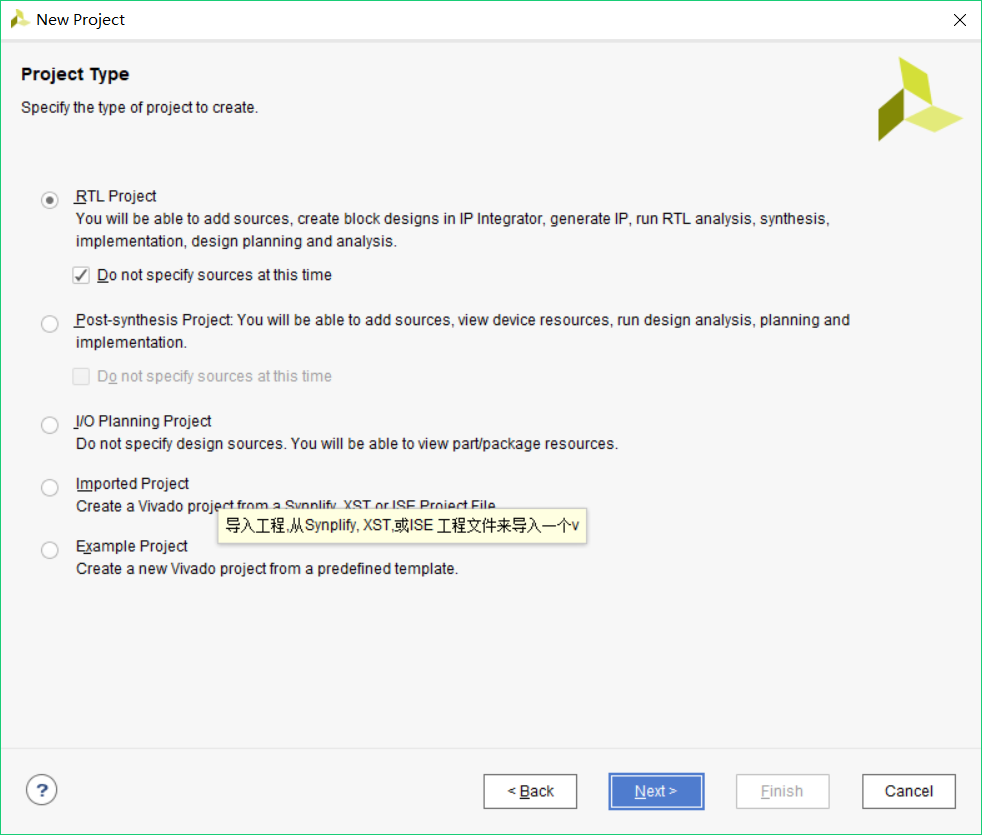

选择RTL project,勾选do not specify sources at this time, 表示以后再配置资源文件

选好了之后点击next

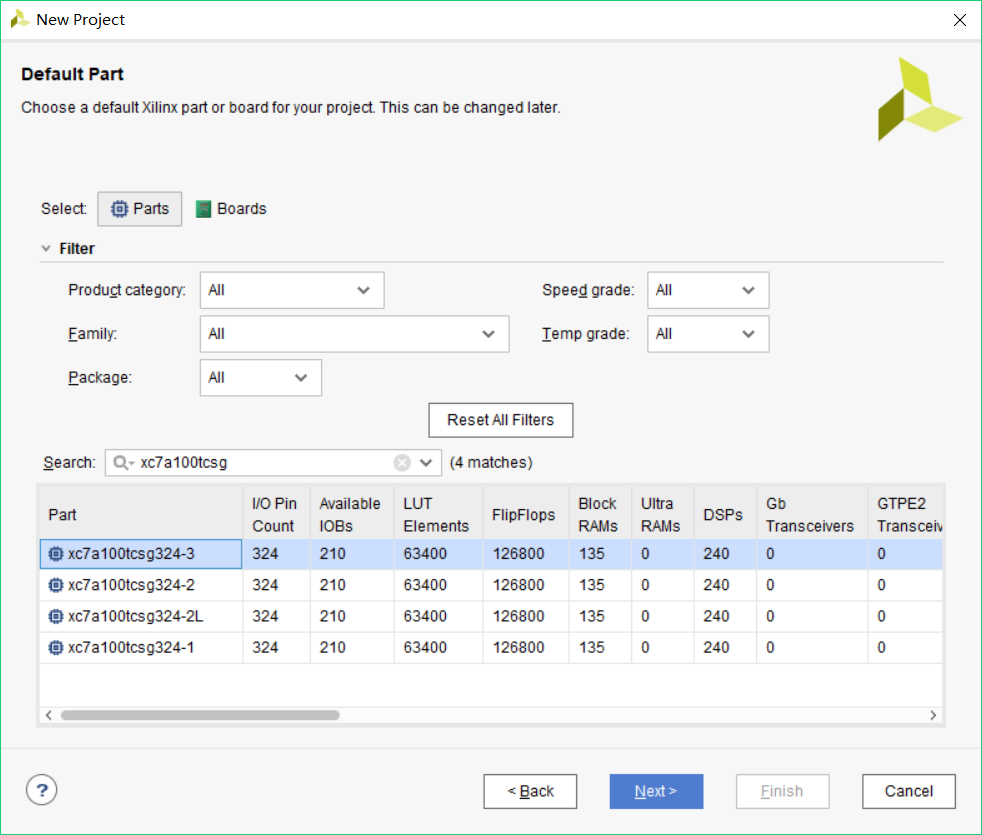

输入你的FPGA板的型号,我的是xc7a100tcsg424

然后点击next

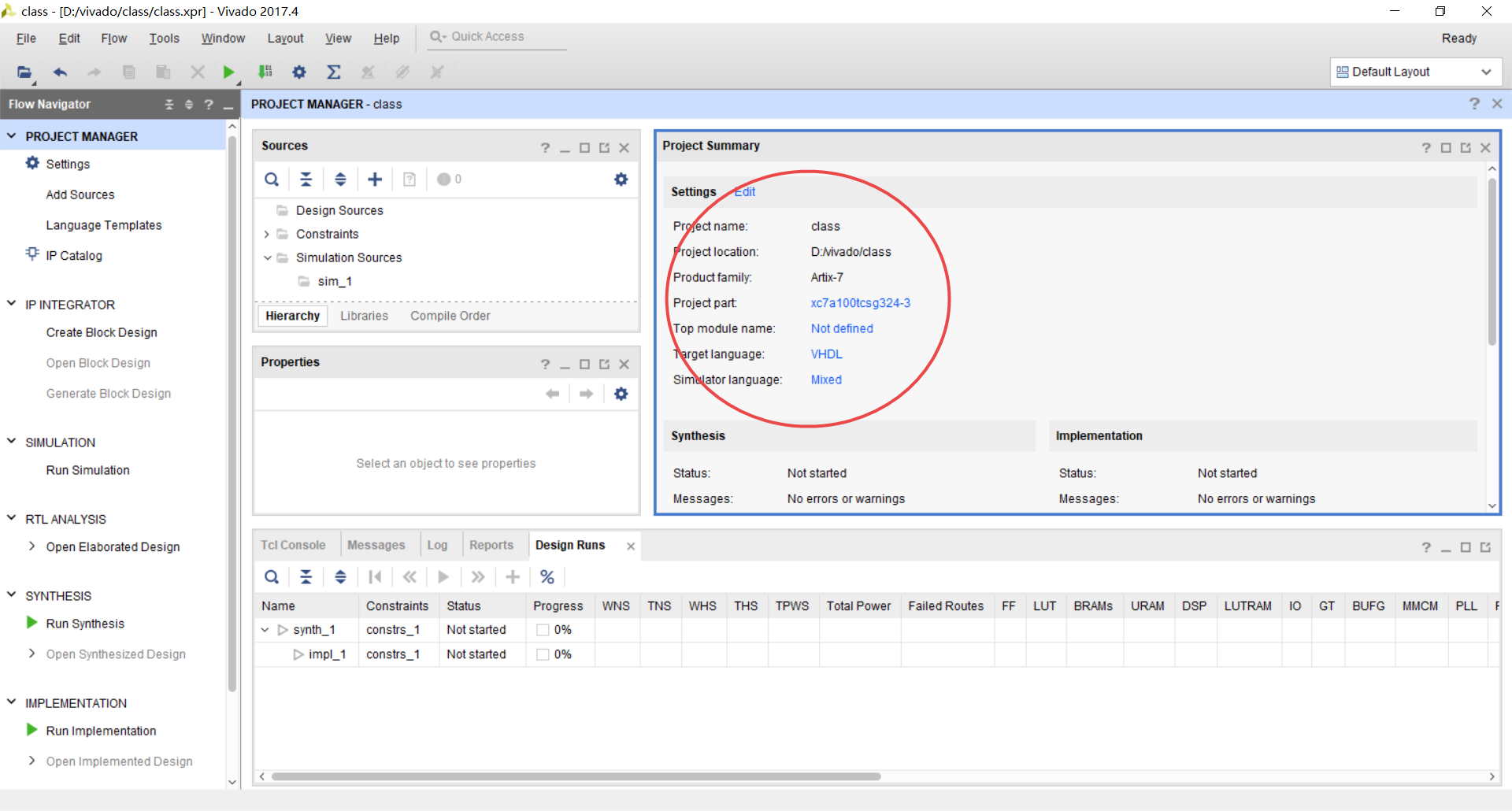

finish之后,如图所示,可以配置语言,这里选择的是VHDL

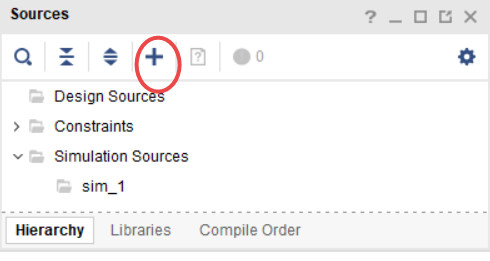

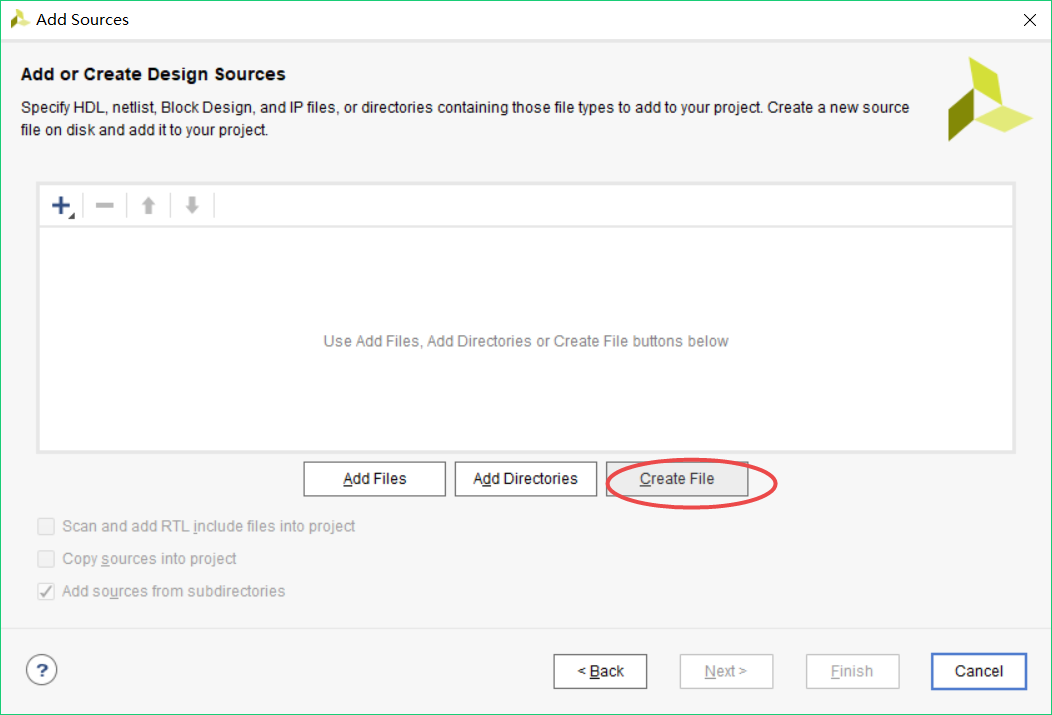

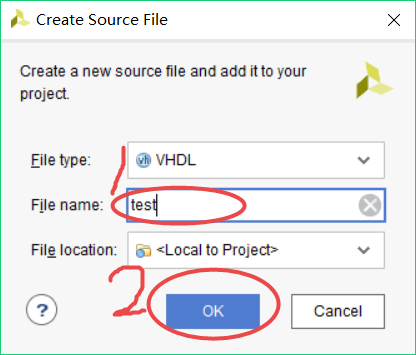

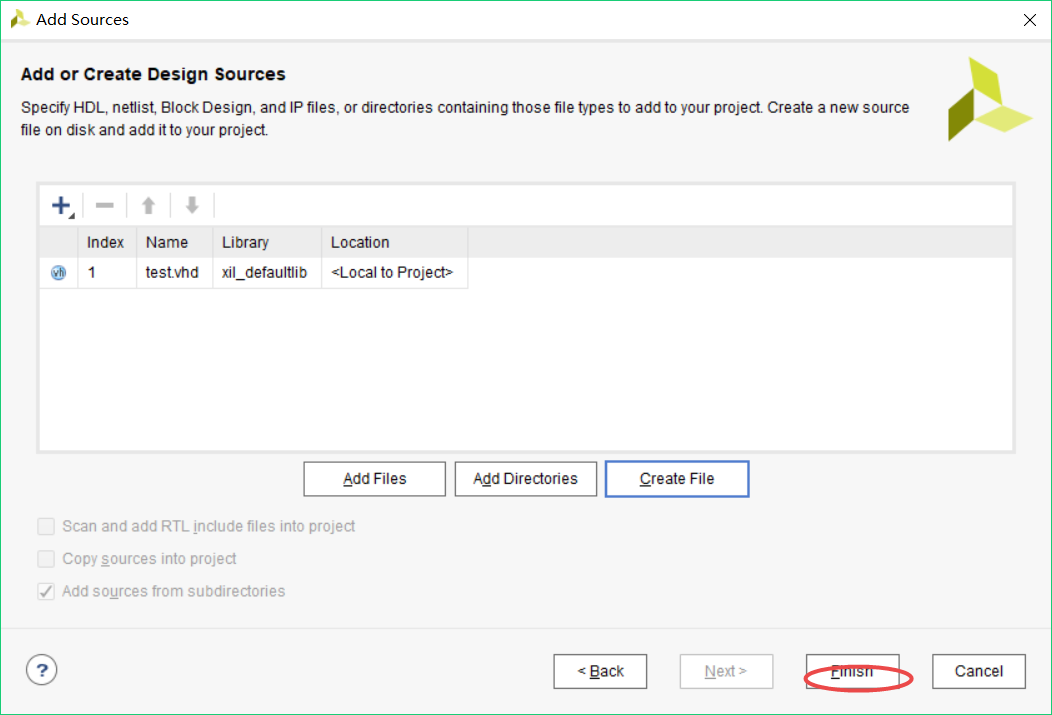

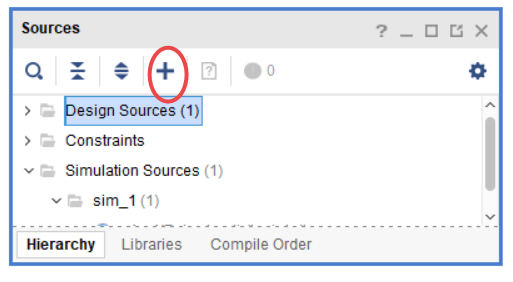

然后我们开始新建/添加文件,点击+

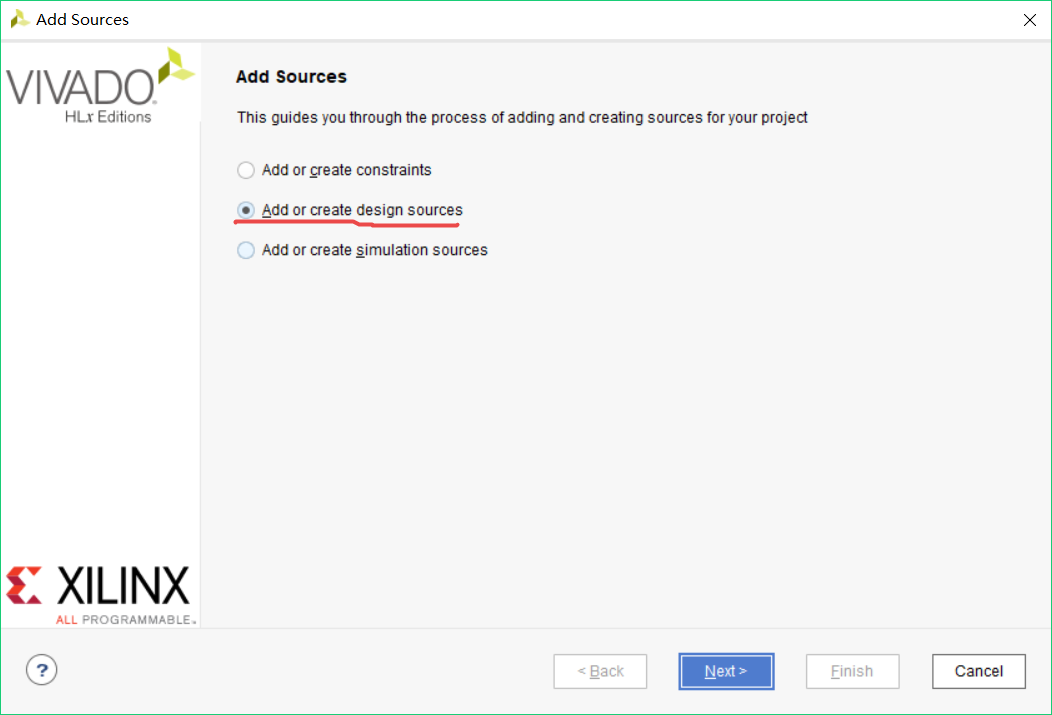

选择add or create design sources

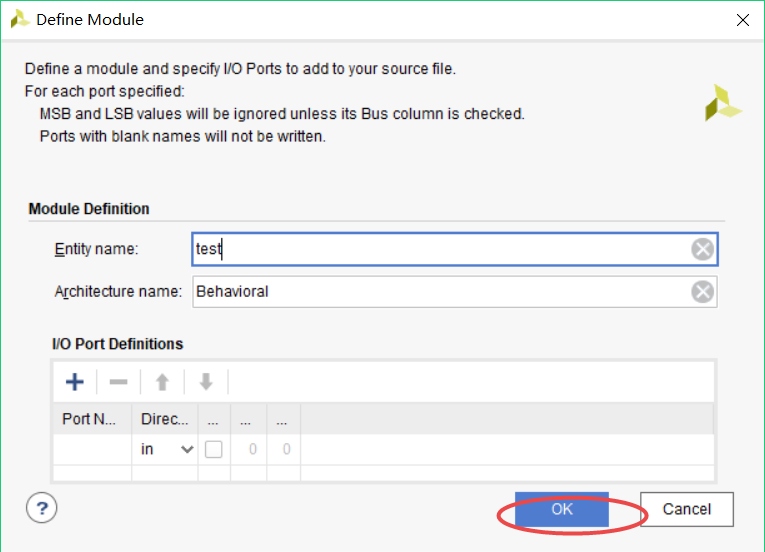

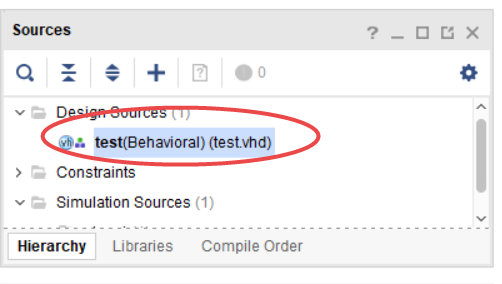

双击你所建立的source之后,就可以开始写程序了

写程序

在这里我提供一个简单的程序

1 | library IEEE; |

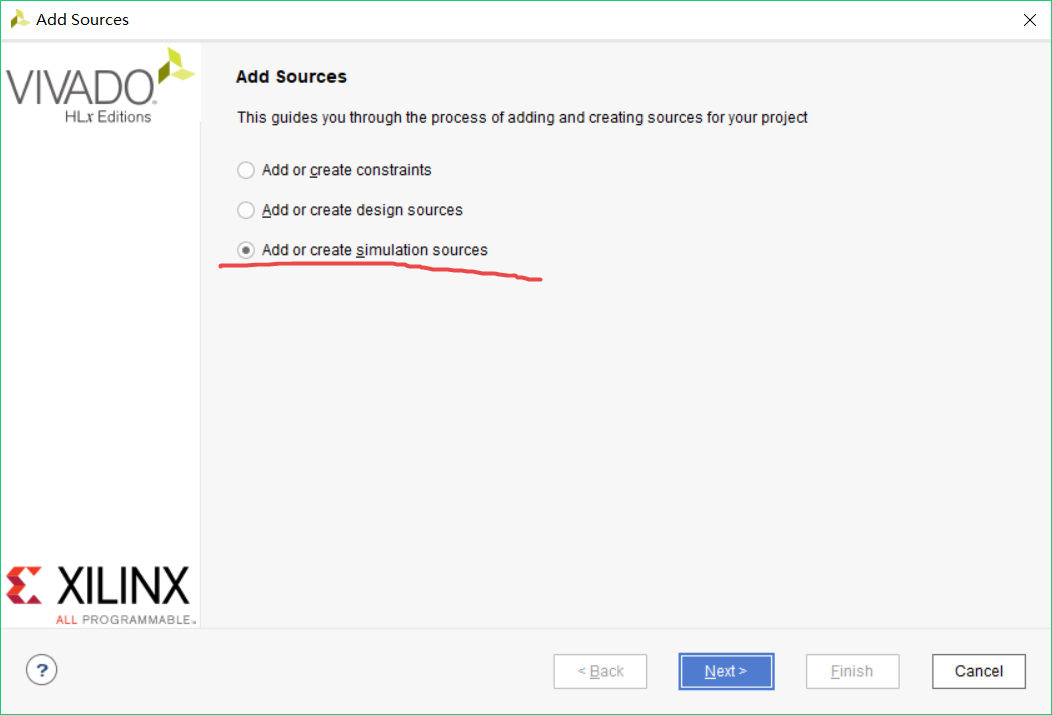

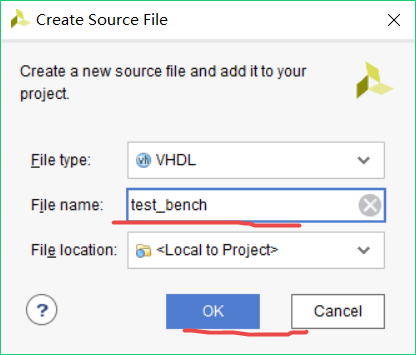

然后我们开始写仿真程序, 同样建立一个仿真文件

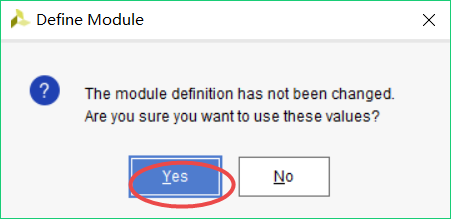

仿真文件的命名通常为test_bench

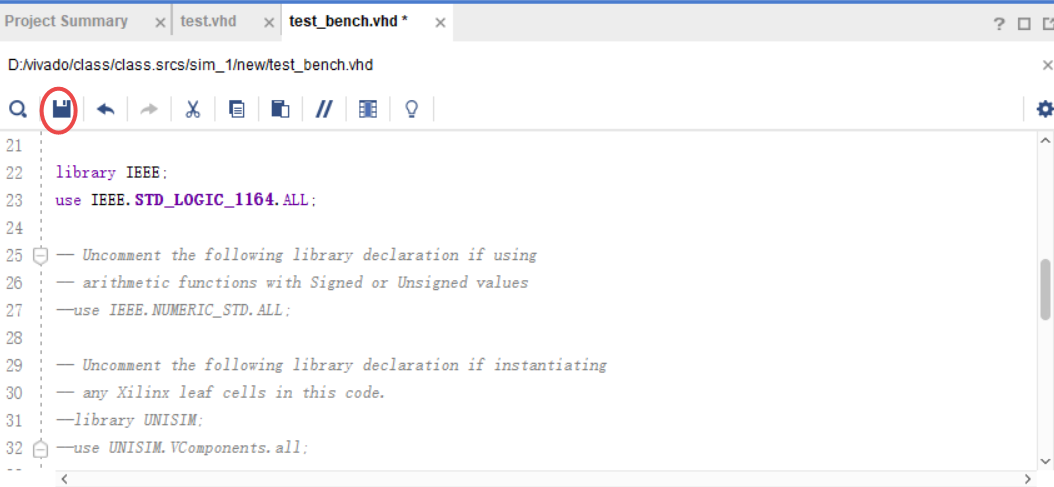

这里我也提供对应的仿真程序,以供参考

1 | library IEEE; |

写完之后点击保存

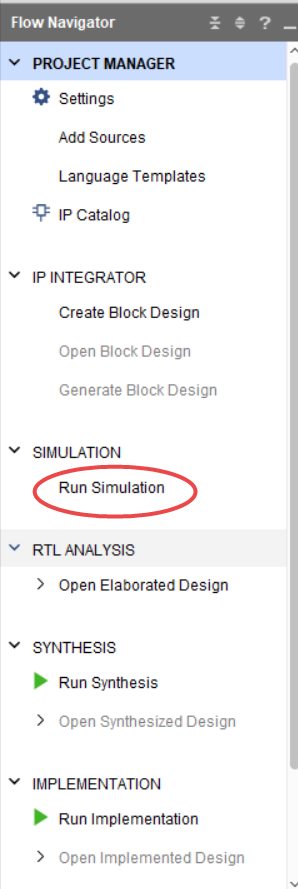

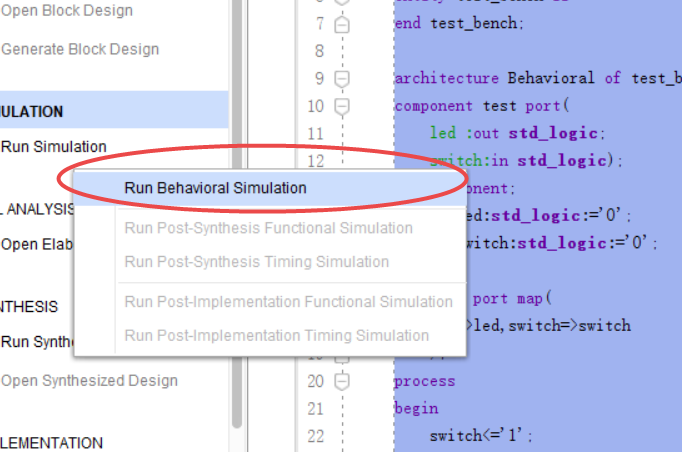

仿真

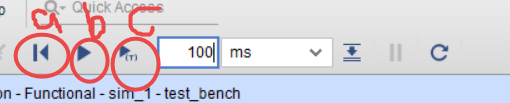

仿真界面的上方有三个键:a是重新开始仿真,b是开始仿真直到点击break(F5), c是仿真指定的时间,我这里设置的是100ms

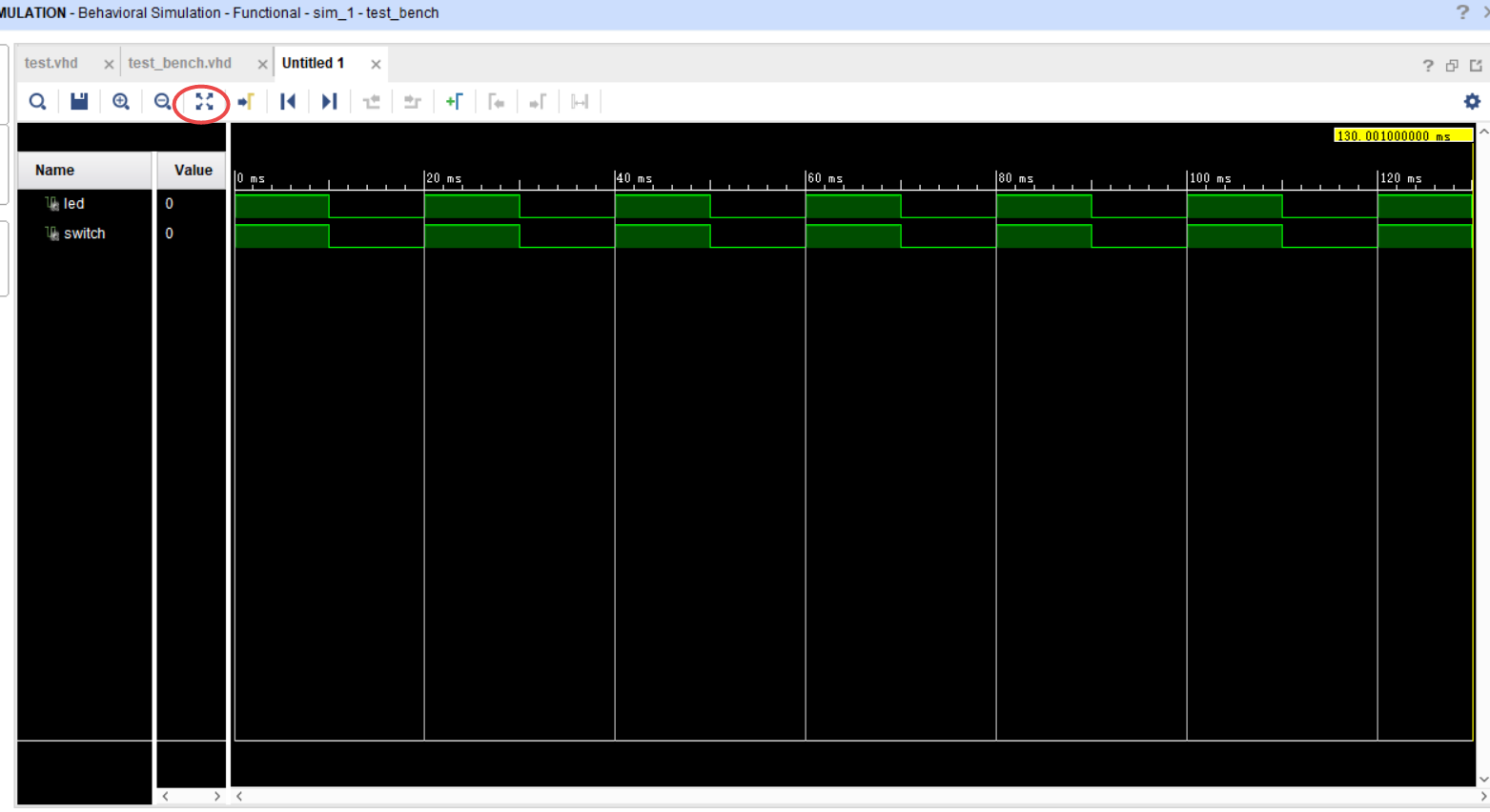

点击红色圆圈里的是看到所有仿真波形

仿真波形没有错误,开始综合

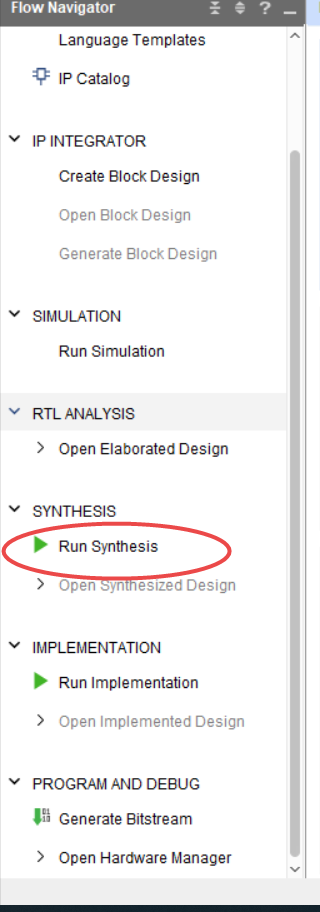

综合

点击 run synthesis, 等待一段时间

跳出一个对话框,点击cancel

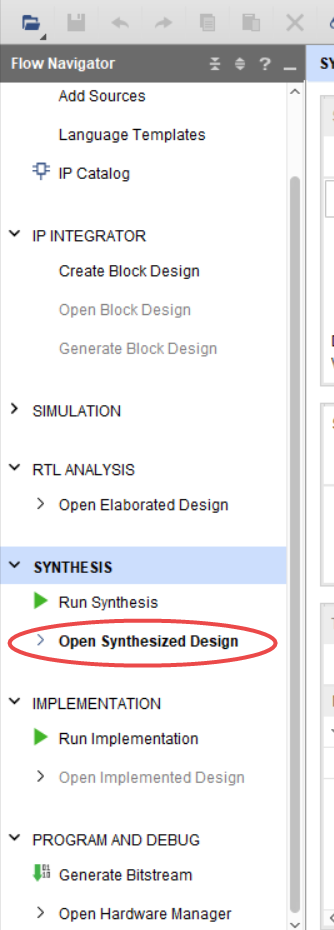

约束

如果你没有现成的约束文件,就自己约束了

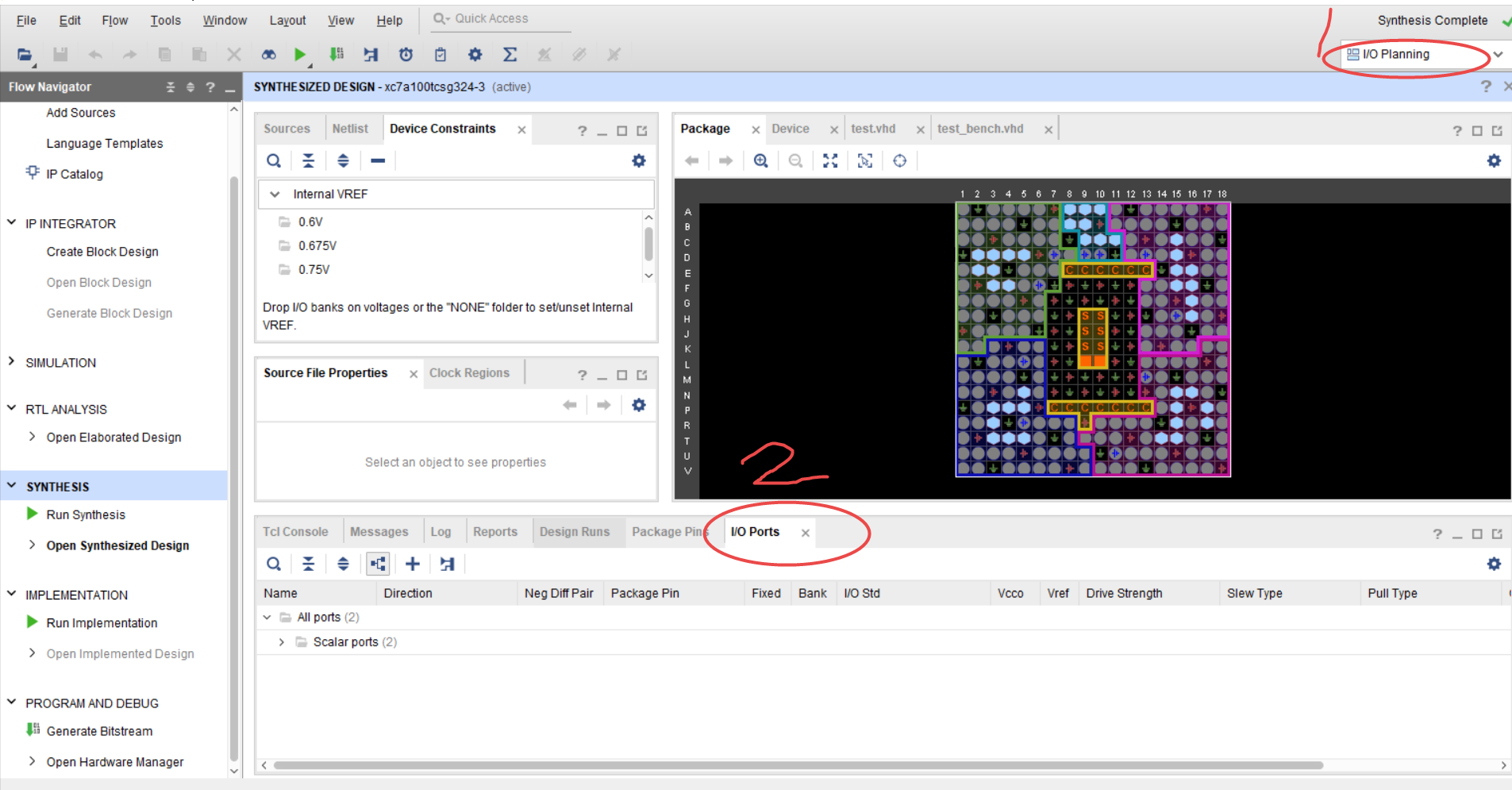

先点击 open synthsized design

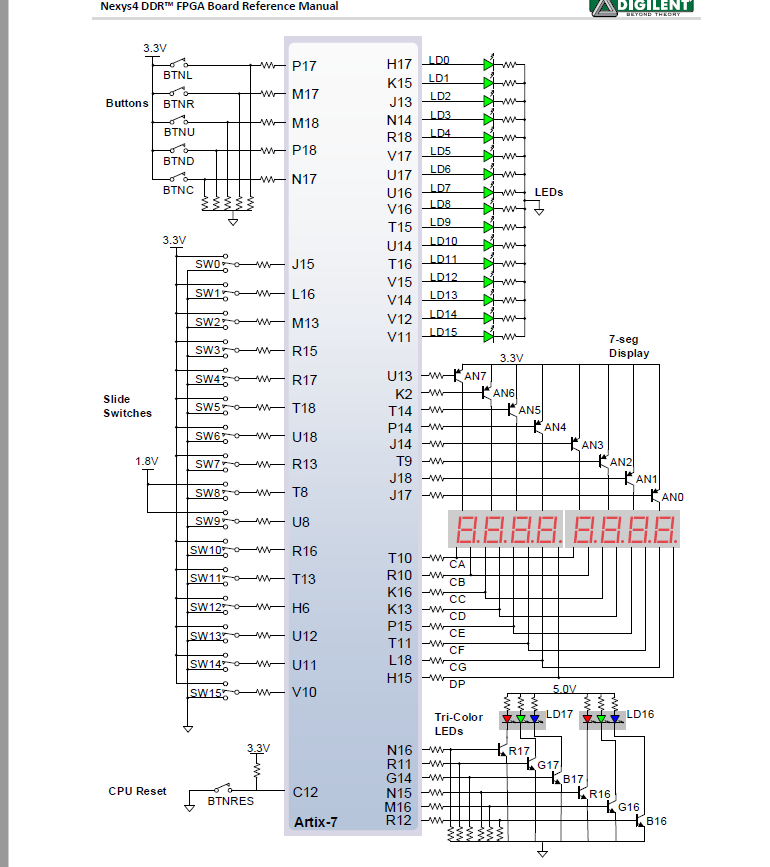

打开开发板的使用指南

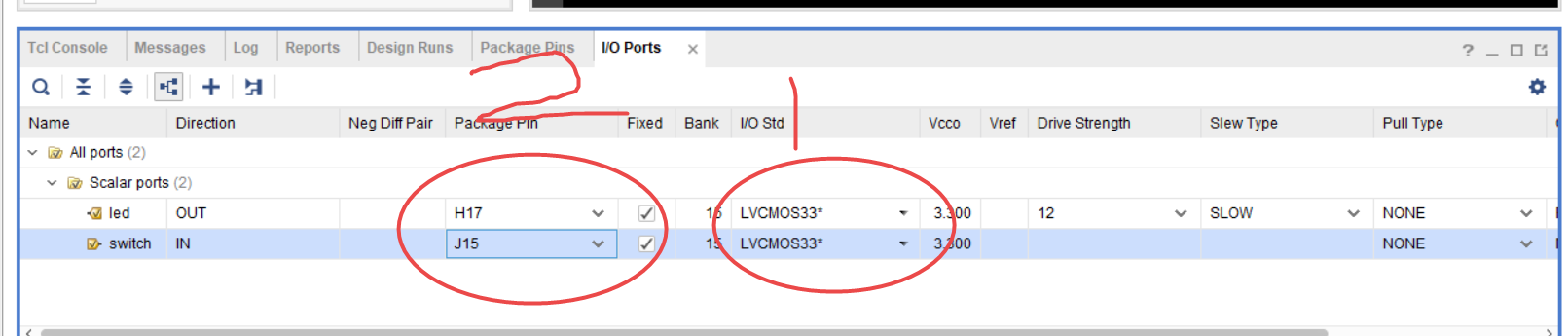

例如:我想约束为

led对应LD0(H17)

switch对应switch0(J15)

约束之后,保存CTRL+S,跳出来对话框,点击确定

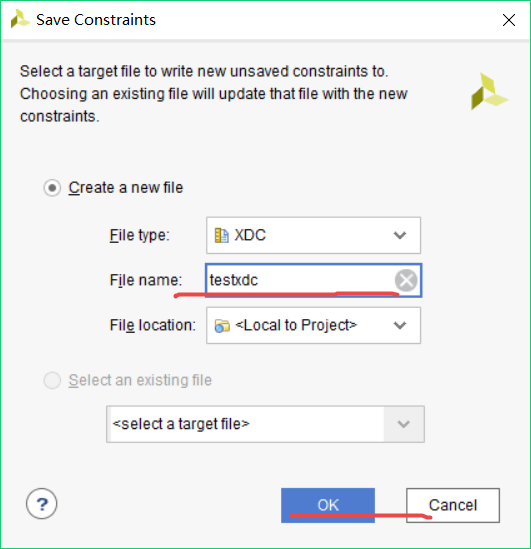

然后为约束文件命名

然后重新执行综合

实现以及生成二进制文件

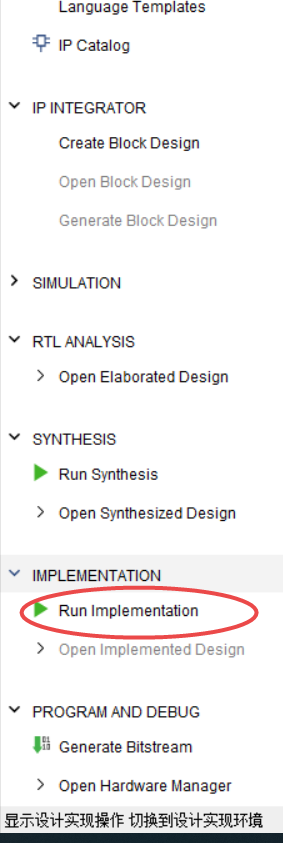

实现

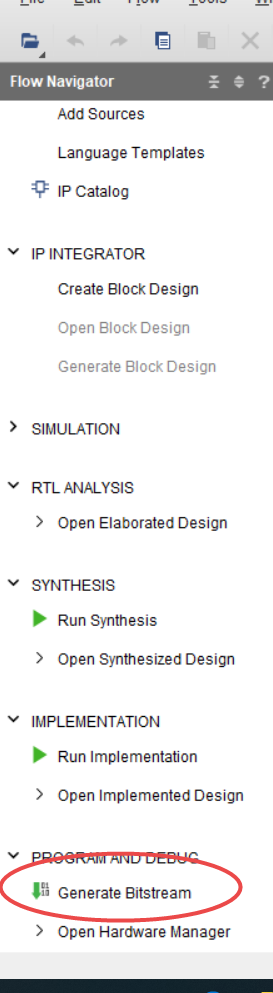

生成二进制文件

然后 open hardware manager

点击open target

点击device program

程序下载完毕后观察实验现象